**Arnaud Virazel**

virazel@lirmm.fr

#### **Arnaud Virazel**

virazel@lirmm.fr

#### Verification versus Test

- To verify the correctness of the design

- Done by simulation, hardware emulation, formal proof

- Performed before fabrication steps

- Responsible of the design quality

- To verify the correctness of the manufactured device

- Done in tow steps:

- Test program generation: performed during the design phase

- Test application: electrical tests applied after manufacturing

- Electrical tests are:

- Applied on each manufactured devices

- Responsible of the device quality

## 4

#### **ICs Production Cost**

#### When Test?

## When Test?

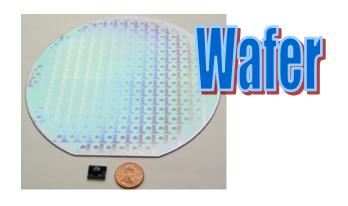

| DUT - Device Under Test                 |                         |                         |             |

|-----------------------------------------|-------------------------|-------------------------|-------------|

| Wafer                                   | Package                 | Board                   | System      |

| Test of the<br>technological<br>process | Parametric test         | "Entrance" test         | System test |

| Test of dies                            | Logic test              | Board test              | In-use test |

|                                         | Aging (burning<br>test) | Finalized board<br>test |             |

|                                         | Full test on samples    | Aging                   |             |

#### **Test Results**

# Results OK OK OK Sequence OK OK OK OK OK

Reality

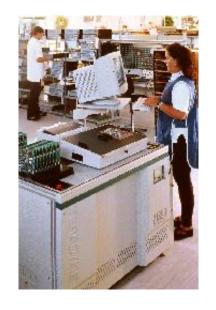

### ATE – Expensive equipment (M\$)

- Testing is possible when one can apply a known stimulus to an entity in a known state and when the known response can be evaluated

- known stimulus: access to the DUT inputs and apply a known value

- ⇒ CONTROLABILITY

- Known response: access to the DUT outputs and comparison with the golden one

- ⇒ OBSERVABILITY

- Error: erroneous observed behavior

- Fault: deviation of the structure from the specifications

- Defect: deviation of the physical realization from the manufacturing specifications

- Failure: malfunction in operation

- Test: fault detection

- Diagnosis: fault localization